# Rapid Development of System-on-Chip (SoC) for Network-Enabled Visible Light Communications

https://doi.org/10.3991/ijes.v6i1.8098

Trio Adiono<sup>(⊠)</sup>, Syifaul Fuada Institut Teknologi Bandung, Indonesia tadiono@stei.itb.ac.id

Rosmianto Aji Saputro Xirka Silicon Technology, Co. Ltd., Bandung, Indonesia

Abstract-Visible Light Communication (VLC) is an emerging optical communication technology with rapid development nowadays. VLC is considered as a compliment and successor of radio-frequency (RF) wireless communication. There are various typical implementations of VLC in which one of them is for exchanging data TCP/IP packets, thus the user can browse the internet as in established Wireless fidelity (Wi-Fi) technology. Briefly, we can call it by Light fidelity (Li-Fi). This paper described the design and implementation of System-on-Chip (SoC) subsystem for Li-Fi application where the implemented SoC consists of hardware (H/W) and software (S/W). In the H/W aspect, Physical Layer (PHY) is made by using UART communication with Ethernet connection to communicate with Host/Device personal-computer (PC). In the S/W aspect, Xillinux operating system (OS) is used. The H/W- as well as S/W-SoC, are realized in FPGA Zybo Zynq-7000 EPP development board. The functional test result shows (without optical channel or Zybo-to-Zybo only) that the implemented SoC is working as expected. It is able to exchange TCP/IP packets between two PCs. Moreover, Ethernet connection has bandwidth up to 83.6 Mbps and PHY layer baud rate has bandwidth up to 921600 bps.

**Keywords**—Light fidelity (Li-Fi), Physical layer, System-on-Chip, Visible Light Communication, Xillinux OS

# 1 Introduction

Mobile data traffic which grows exponentially for the last two decades has caused extreme wireless network usage. As the impacts, the available RF spectrum will be greatly reduced. Then the channel interference will be higher [1]. The year 2021 worldwide estimated there are more than 49 exabytes (Note, 1 EB = 1 billion gigabytes) of data traffic from the mobile-network in every month [2]. One solution is to replace the common RF-based technologies (like Wi-Fi) with another technology which employs beyond the RF spectrum. Visible light (380 nm – 780 nm) is considered spectrum to be employed for high-speed internet access purpose with no elec-

tromagnetic interference, highly secure communication, no licensed bandwidth, and no health concern [3], this technology commonly called as Li-Fi [4].

Li-Fi system is built by two blocks: the digital part and the analog part. Similar with Wi-Fi, the Li-Fi must offer an extremely high-speed internet connection to the user. Therefore, a very fast microprocessor system is needed for Li-Fi application in order to process the fastest data. The field-programmable gate array (FPGA) is more feasible to utilize compared to general microcontroller for high-speed DSP application [5]. That is why this work uses SoC platform as a digital processor in VLC system. The SoC is an integrated circuit containing all components of an electronic system or computer on a single-chip. With SoC technology, the bulky VLC system (because of using commercial off-the-shelf devices) as reported so far, will be minimized drastically in terms of size [6]. SoC VLC is an emerging technology.

In previous research, we have implemented SoC VLC but it is functionalized for high-speed data acquisition only in receiver system [7]. In this paper, the designed SoC architecture focuses to process the 'TCP/IP packet' for Li-Fi applications. The Specifications for SoC are able to: 1) exchange data between two computers; 2) convert data packet to bit-level transmission; and transmit the data with maximum *baud rate* (921600 bps) by UART communication. The defined specifications will be the reference in design and implementation phase (Section II). Whereas the discussion performance tests are presented in Section III.

## 2 Methodology

#### 2.1 Network Topology and Data Exchange Mechanism

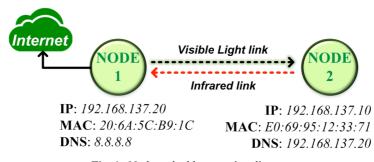

Based on the defined system specifications, there are two units of the personal computer node to be used, for Host and then Device function. Commonly, network topology for two nodes employs point-to-point (P2P) topology [8]. In order for this two nodes that able to exchange data through the links, it is necessary to set the appropriate IP address, DNS Server, MAC address, and Gateway address. The selection of IP Address and MAC Address are arbitrary, while DNS is set with 8.8.8.8 (Google's public DNS). The connection design for two nodes is depicted in Fig. 1.

Fig. 1. Node and address setting diagram

The data exchanges (TCP/IP packet) between two nodes can be classified into two sides, *i.e.* device to host and device to device. In this work, the PHY layer development is not focused on IEEE 802.15.7 standard compliance. Therefore, we used Reed-Solomon (RS) and UART.

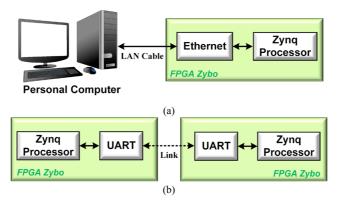

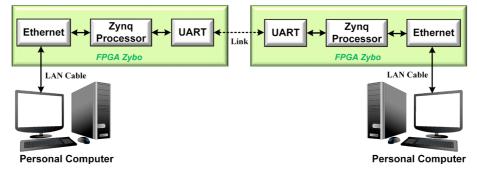

At the personal computer to FPGA Zybo part, the data exchange is done by using Ethernet connection via LAN cable where it is chosen because of the common wired internet connectivity. Furthermore, FPGA Zybo is equipped with complete peripherals that also supports Ethernet connexion. The connection diagram is shown in Fig. 2(a). While for Zybo to Zybo part, the data exchange is done by using UART communication as illustrated in Fig. 2(b). The complete diagram is shown in Fig. 3.

As described previously, the P2P topology for this work is used two FPGA Zybo boards and two personal computers. The following a step by step for the IP Address and DNS setting in Windows 2010 OS: Start  $\rightarrow$  Settings  $\rightarrow$  Network and Internet  $\rightarrow$ Ethernet  $\rightarrow$  Change adapter options  $\rightarrow$  Double-click Ethernet  $\rightarrow$  Double-click Internet Protocol version 4 (TCP/IP v4) until the properties appears as visualized in Fig. 4(a), while for Linux OS (in FPGA Zybo), IP Address and DNS setting is by rightclicked on network icon (in the upper right corner) then 'Edit Connections' as visualized in Fig. 4(b).

Fig. 2. The diagram of data exchanges: (a) device to host; (b) device to device

Fig. 3. Complete diagram of data exchange mechanism

| letworking                                   | Sharing                                                                                                                                                                                          | Connection name: Wired connection 1                                                                                    |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Connect u                                    | Internet Protocol Version 4 (TCP/IPv4) Properties X                                                                                                                                              | Gonnect automatically<br>Wired 802.1x Security IPv4 Settings                                                           |

| This conn                                    | General<br>You can get IP settings assigned automatically if your network supports<br>this capability. Otherwise, you need to ask your network administrator<br>for the appropriate IP settings. | Method: Manual                                                                                                         |

|                                              | ○ Obtain an IP address automatically    ● Use the following IP address:    IP address:  192 . 168 . 137 . 20    Subett mask:  255 . 255 . 0                                                      | Address  Netmask  Gateway  Add    192.168.137.10  255.255.255.0  192.168.137.20  Deleter                               |

| <<br>Descript<br>Transm<br>wide ar<br>across | Default gateway:  192 . 168 . 137 . 10    Obtain DNS server address automatically     @ Use the following DNS server:  8 . 8 . 8    Preferred DNS server:  8 . 8 . 8    Alternate DNS server:    | DNS servers:<br>Search domains:<br>DHCP client ID:<br>Require IPv4 addressing for this connection to comple<br>Routes. |

|                                              | OK Cancel                                                                                                                                                                                        | ☑ Available to all users Cancel Save                                                                                   |

Fig. 4. Screenshot of configuration setting for: (a) IP address and DNS address in Windows 10 OS; (b) IP address and Gateway in Linux OS

Ethernet connection has been already activated, so there is no need to configure it manually in FPGA Zybo. Fig. 5 shows the *ifconfig* command in FPGA Zybo, it can be shown that *eth0* (first Ethernet interface) has been configured.

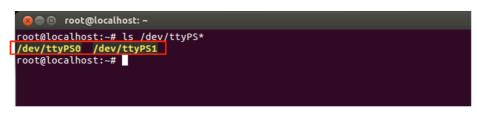

For the universal asynchronous receiver-transmitter (UART) communication, the peripheral is generated by using Vivado 2015.1 software. Moreover, the DTB file is also need to be modified so Xillinux OS can recognize the added UART peripherals. Fig. 6 visualizes the UART enabling process, whereas Fig. 7 visualizes the UART peripheral that has been created.

| eth0    | Link encap:Ethernet HWaddr e0:69:95:12:33:71<br>inet addr:192.168.137.10 Bcast:192.168.137.255 Mask:255.255.255<br>inet6 addr: fe80::e269:95ff:fe12:3371/64 Scope:Link<br>UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1<br>RX packets:11191 errors:0 dropped:0 overruns:0 frame:0<br>TX packets:1153 errors:0 dropped:0 overruns:0 carrier:0<br>collisions:0 txqueuelen:1000<br>RX bytes:1625933 (1.6 MB) TX bytes:90960 (90.9 KB)<br>Interrupt:54 Base address:0xb000 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lo      | Link encap:Local Loopback<br>inet addr:127.0.0.1 Mask:255.0.0.0<br>inet6 addr: ::1/128 Scope:Host<br>UP LOOPBACK RUNNING MTU:65536 Metric:1<br>RX packets:2160 errors:0 dropped:0 overruns:0 frame:0<br>TX packets:2160 errors:0 dropped:0 overruns:0 carrier:0<br>collisions:0 txqueuelen:0<br>RX bytes:156968 (156.9 KB) TX bytes:156968 (156.9 KB)                                                                                                                     |

| root@lo | ocalhost:~#                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Fig. 5. Performance test for device to host scheme

**Fig. 6.** The peripherals activation on Vivado 2015.1, the DTB must be generated from the DTS source code (Please see its code in the supplementary file of this paper)

Fig. 7. UART peripheral (*ttyPS0*), we can see that .*ttyPS1* already exists by default

#### 2.2 Xillinux OS

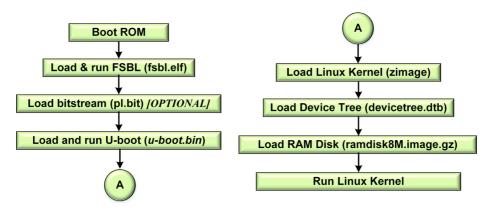

In previous work, we have developed MAC Layer software that is written in Python script [9], to execute this programs, we need an OS. The FPGA Zybo board has ARM-based processor that capable to run the Linux OS. There are several Linux OS distributions can be run by FPGA Zybo, one of them is Xillinux OS that is chosen in this work because of it can communicate directly with FPGA fabrics and also able to access Ethernet and UART peripherals [10]. To perform the booting process, FPGA Zybo needs to perform several boot stages as depicted in Fig. 8.

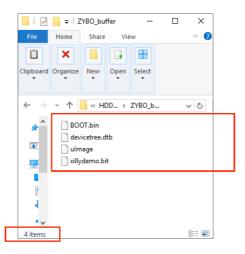

The FPGA Zybo employed SD Card media storage to boot Xillinux OS. Therefore, it should be formed into 2 partitions: *FAT32* and *EXT4* file system. The *FAT32* partition comprises *u-boot.bin* (merged into a *boot.bin file*), *FSBL file*, Linux Kernel

(named as *uImage*), and *Bitstream PL* (written as *xillydemo.bit*). While **EXT4** partition comprises Linux RAM Disk. Those files are generated by using Vivado 2015.1 software and placed in the **FAT32** partition. Generated files should look like visualized in Fig. 9. If the structure of these required files is correct, the SD Card can be booted well and vice versa.

Fig. 8. Flowchart of Linux booting in FPGA Zybo, reproduced from [11]

Fig. 9. File structure of Xillinux OS

#### 2.3 Forward Error Correction (FEC)

The FEC is a method to recover error from data transmission by sending redundant data. As stated by IEEE 802.15.7 standard, the FEC for PHY layer of VLC is RS code or RS(n,k) method [12]. In brief, the principle of work: the data entered through the RS encoder will occur the addition of bits to overcome the error. Later, the received data will also be recovered and re-read by the RS. We used RS(64,32) means 64-bit of block length, 32-bit of input data length, and 16-bit of parity.

In this work, FEC RS is created by using freely available online library that is written in Python script (please see the FEC RS open source code in the following link: <u>https://github.com/jkent/minimodem-crypt/blob/master/minimodem-crypt/reedsolo.py</u>).

### 2.4 Overall Design of SoC

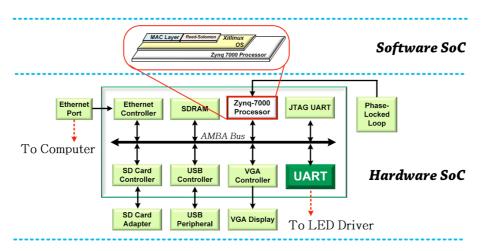

Fig. 10. Architecture of the designed SoC for network-enabled VLC

| Register Base Address | Description           |  |  |

|-----------------------|-----------------------|--|--|

| E000_0000, E000_1000  | UART Controllers 0, 1 |  |  |

| E000_2000             | USB Controllers 0     |  |  |

| E000_B000             | Ethernet Controller 0 |  |  |

| F800_6000             | SDRAM                 |  |  |

| E010_0000             | SD Card Controller    |  |  |

| 5000_1000             | VGA Controller        |  |  |

Table 1. The use of register address mapping

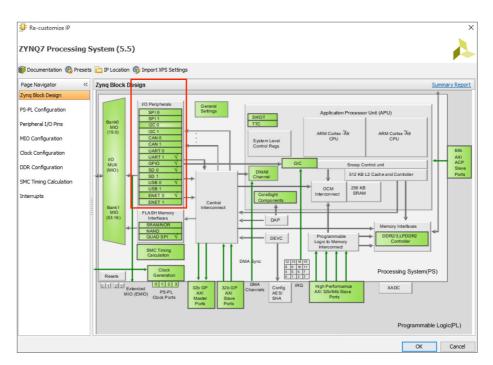

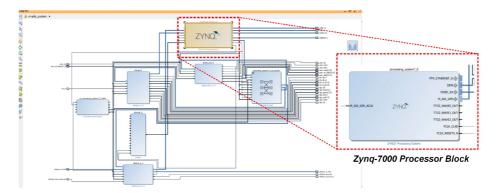

Fig. 11. Implementation of Zync-7000 processor blocks on FPGA Zybo

The designed SoC as illustrated in Fig. 10 consists of two parts: Software (S/W) and Hardware (H/W). The S/W part comprised operating system, Reed-Solomon software, and MAC Layer software while H/W part comprised the components used, register settings which used to access the H/W as shown in Table 1 and design architecture. The implementation of processor block is done by using Vivado 2015.1 software, this block will run Xillinux OS, process the MAC layer part, and execute the RS code.

# 3 Results

#### 3.1 Functionality test of Xillinux OS

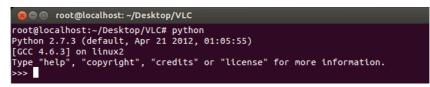

The functionality test of Xillinux OS ensures that it is ready to be employed in developing the required software include booting up as visualized in our previous research [13], loading the standard user interface as depicted in [9], and running the Python script as shown in Fig. 12.

Fig. 12. The Python programs can be run through the Terminal

#### 3.2 Bandwidth of Ethernet and UART

In this work, we performed two measurements: bandwidth of Ethernet and UART. The Ethernet bandwidth measurement is done by using *iperf* tool as shown in Fig. 13. We obtained 83.6 Mbps of average bandwidth.

| IL. |      |             | 100.1 | 31.20 | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |       | connecced we |

|-----|------|-------------|-------|-------|-----------------------------------------|-------|--------------|

| ]   | ID]  | Interval    |       | Trans | sfer                                    | Bandy | width        |

| I   | 3]   | 0.0- 2.0    | sec   | 20.5  | MBytes                                  | 86.0  | Mbits/sec    |

| Ι   | 3]   | 2.0- 4.0    | sec   | 19.6  | MBytes                                  | 82.3  | Mbits/sec    |

| Ι   | 3]   | 4.0- 6.0    | sec   | 20.0  | MBytes                                  | 83.9  | Mbits/sec    |

| Ι   | 3]   | 6.0- 8.0    | sec   | 19.9  | MBytes                                  | 83.4  | Mbits/sec    |

| Ι   | 3]   | 8.0-10.0    | sec   | 19.8  | MBytes                                  | 82.8  | Mbits/sec    |

| Ι   | 3]   | 10.0-12.0   | sec   | 20.0  | MBytes                                  | 83.9  | Mbits/sec    |

| Ι   | 3]   | 12.0-14.0   | sec   | 19.8  | MBytes                                  | 82.8  | Mbits/sec    |

| Ι   | 3]   | 14.0-16.0   | sec   | 19.9  | MBytes                                  | 83.4  | Mbits/sec    |

| Ι   | 3]   | 16.0-18.0   | sec   | 19.8  | MBytes                                  | 82.8  | Mbits/sec    |

| Γ   | 3]   | 18.0-20.0   | sec   | 20.0  | MBytes                                  | 83.9  | Mbits/sec    |

| Ι   | 3]   | 0.0-20.0    | sec   | 199   | MB <u>y</u> tes                         | 83.5  | Mbits/sec    |

| Г   | oot@ | localhost:~ | /Docu | ments | 5#                                      |       |              |

|     | -    |             |       |       |                                         |       |              |

Fig. 13. Measurement of Ethernet bandwidth with iperf tool

While UART bandwidth measurement is done by using Python script which is sending serial data in certain *baud rate*. We obtained 921600 bps of maximum *baud rate* and it can be lowered down to 115200 considering to the capability of the LED driver input frequency.

|   | Bandwidth measurement of UART                           |

|---|---------------------------------------------------------|

| ſ | root@localhost:~/Desktop/VLC# python pure.py/dev/ttyPS1 |

|   | Baudrate: 115200 bps                                    |

|   | hello world! 0                                          |

|   | hello world! 1                                          |

|   | hello world! 2                                          |

|   | hello world! 3                                          |

|   | hello world! 4                                          |

|   | hello world! 5                                          |

|   | hello world! 6                                          |

|   | hello world! 7                                          |

|   | hello world! 8                                          |

|   | hello world! 9                                          |

|   | hello world! 10                                         |

|   | root@localhost:~/Desktop/VLC# python                    |

|   | Baudrate: 921600 bps                                    |

|   | hello world! 0                                          |

|   | hello world! 1                                          |

|   | hello world! 2                                          |

|   | hello world! 3                                          |

|   | hello world! 4                                          |

|   | hello world! 5                                          |

|   | hello world! 6                                          |

|   | hello world! 7                                          |

|   | hello world! 8                                          |

|   | hello world! 9                                          |

|   | hello world! 10                                         |

|   | hello world! 11                                         |

|   | root@localhost:~/Desktop/VLC#                           |

#### 3.3 Overall Test

We have performed functional test of RS, the input of RS is TCP/IP packet data where its input is always an integer. The decoding result of RS is then compared with the input to find the error value. The result of performance test shows that the implemented RS can detect error occurs in the communication system.

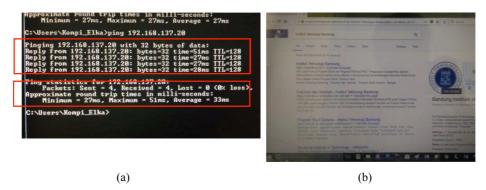

The evaluation of overall system is by doing ping and browsing the internet. Fig. 14(a) visualizes the ping testing result, we obtained 33 milliseconds of average latency. Fig. 14(b) proves that internet browsing successfully demonstrated (in this term, we used Google search engine). Therefore, FPGA-based VLC (Li-Fi) is able to exchange network packet (TCP/IP). Thus, it allows users to "surfing" and "browsing" to the internet such as Wi-Fi technology. It should be noted that in this evaluation, we test our SoC by following scenario: FPGA Zybo transmitter to FPGA Zybo receiver. It means that analog front-end module is not connected yet.

Fig. 14. Screenshot of: (a) Ping test result between two computers (Host-to-device); (b) successful internet browsing in searching the keywords of "Institut Teknologi Bandung"

### 4 Conclusions

We can conclude several key points for this work, i.e. 1) SoC subsystem has been designed and carefully implemented, and also already demonstrated successfully to perform Ping and browsing the internet; 2) the average of Ethernet bandwidth is 83.6 Mbps; 3) the maximum bandwidth of UART communication is 921600 bps. For future work, we will integrate our DSP (FPGA Zybo) with analog front-end part.

This work has strong correlation with the works. To track our research results and to know the relationship among others, the readers can find the following reference **[14-35]**. Later, the PHY layer on our Li-Fi subsystem can also be improved by designing RS based on H/W, then adding *RLL 8B10B* and Manchester Encoding.

### 5 Acknowledgment

This research is one part of the big project entitled "Machine-to-machine Communication (M2M) based on Visible Light Communication (VLC)" was funded by the Ministry of Research, Technology and Higher Education of the Republic Indonesia via *Kerjasama Luar Negeri* (KLN) scheme with Pukyong National University (PKNU), Republic of South Korea (Contract No. 009/SP2H/LT/DRPM/IV/2017).

### 6 References

- D. Tsonev, S. Videv, and <u>H. Haas</u>, "Light fidelity (Li-Fi): towards all-optical networking", *Proc. SPIE 9007, Broadband Access Communication Technologies VIII*, 900702, February 2014. <u>https://doi.org/10.1117/12.2044649</u>

- [2] Cisco Visual Networking Index: Global Mobile Data Traffic Forecast Update, 2016-2021 White Paper, [Online] Available at <u>https://www.cisco.com/c/en/us/solutions/collateral/</u> service-provider/visual-networking-index-vni/mobile-white-paper-c11-520862.html.

- [3] S. Fuada, "Design and Implementation of Analog Front-End Transceiver Module for Visible Light Communication System," M.T. thesis, Dept. Elect. Eng., School of Electrical Engineering and Informatics, Institut Teknologi Bandung, Bandung, Indonesia, 2017.

- [4] S. Fuada, A.P. Putra, Y. Aska, A. Pradana, E. Setiawan, and T. Adiono, "Implementasi Perangkat *Digital Signal Processing* untuk Sistem Komunikasi Cahaya Tampak," *Unpublished.*

- [5] T. Adiono, S. Fuada, R.A. Saputro, and M. Luthfi, "Internet Access over Visible Light," Unpublished.

- [6] T. Lang, Z. Li, G. Chen, and A. Wang, "LED-based Visible Light Communication and Positioning Technology and SoCs," [Online] Available at <u>https://pdfs.semanticscholar.org/8ba8/22b7e67bb1d57dc5d33d27db9c4b036b7c16.pdf.</u>

- [7] A. P. Putra, S. Fuada, Y. Aska, and T. Adiono, "System-on-Chip Architecture for High-Speed Data Acquisition in Visible Light Communication System," *Proc. of the IEEE Int. Symposium on Electronics and Smart Devices* (ISESD), pp. 63-67, October 2016 <u>https://doi.org/10.1109/ISESD.2016.7886693</u>

- [8] Y. Wang, N. Chi, Y. Wang, L. Tao and J. Shi, "Network architecture of a high-speed visible light communication local area network," *IEEE Photonics letters*, Vol. 27(2), pp. 197-200, January 2015.

- [9] T. Adiono. S. Fuada, M. Luthfi, and R.A. Saputro, "MAC Layer Design for Network-Enabled Visible Light Communication Systems Compliant with IEEE 802.15.7," *EAI Endorsed Transactions on Energy Web and Information Technology*, Vol.4(14), 2017. https://doi.org/10.4108/eai.4-10-2017.153163

- [10] Getting started with Xillinux for Zynq-7000 EPP. [Online] Available at http://xillybus.com/downloads/doc/xillybus\_getting\_started\_zynq.pdf.

- [11] Wikidot, "ZC702 boot from flash" [Online] Available at <u>http://xilinx.wikidot.com/zc702-boot-from-flash</u>.

- [12] IEEE Computer Society, "IEEE Standard for Local and metropolitan area networks Part 15.7," Short-Range Wireless Optical Communication Using Visible Light, New York: IEEE.2011

- [13] T. Adiono, R.A. Saputro, M. Luthfi, and S. Fuada, "A Real-time Wireless Video Streaming based on VLC Technology using FPGA," Unpublished.

- [14] T. Adiono, A. Pradana, R.V.W. Putra, and S. Fuada, "Analog Filters Design in VLC Analog Front-End Receiver for Reducing Indoor Ambient Light Noise," *Proc. of the IEEE Asia Pacific Conf. on Circuit and Systems* (APCCAS), pp. 581-584, October 2016. https://doi.org/10.1109/APCCAS.2016.7804058

- [15] S. Fuada, A.P. Putra, Y. Aska, and T. Adiono, "Trans-impedance Amplifier (TIA) Design for Visible Light Communication (VLC) using Commercially Available OP-AMP," Proc. of the 3<sup>rd</sup> Int. Conf. on Information Tech. Computer, and Electrical Engineering (ICITACEE), pp. 31-35, October 2016. https://doi.org/10.1109/ICITACEE.2016.7892405

- [16] S. Fuada, T. Adiono, A. P. Putra, and Y. Aska, "A Low-cost Analog Front-End (AFE) Transmitter Designs for OFDM Visible Light Communications," *Proc. of the IEEE Int. Symposium on Electronics and Smart Devices* (ISESD), pp. 371-375, October 2016. https://doi.org/10.1109/ISESD.2016.7886750

- [17] S. Fuada, and T. Adiono, "Rancang Bangun Layer Fisik Visible Light Communication Pada Sistem Transmisi Audio," *J. INFOTEL*, Vol. 9(3), pp. 352-360, August 2017. DOI: https://doi.org/10.20895/infotel.v9i3.288.

- [18] T.Adiono and S. Fuada, "Desain dan Implementasi LED Driver Linier untuk Aplikasi Visible Light Communication," Unpublished.

- [19] S. Fuada, "Kajian Aspek Security pada Jaringan Informasi dan Komunikasi Berbasis Visible Light Communication," J. INFOTEL, Vol. 9(1), pp. 108-121, August 2017. DOI: <u>https://doi.org/10.20895/infotel.v9i1.163</u>.

- [20] S. Fuada, A.P. Putra, Y. Aska and T. Adiono, "A First Approach to Design Mobility Function and Noise Filter in VLC System Utilizing Low-cost Analog Circuits," *Int. J. of Recent Contributions from Engineering, Science, and IT* (iJES), Vol. 5(2), pp. 14 – 30, 2017. https://doi.org/10.3991/ijes.v5i2.6700

- [21] S. Fuada, A.P. Putra, and T. Adiono, "Analysis of Received Power Characteristics of Commercial Photodiodes in Indoor LoS Channel Visible Light Communication," *Int. J. of Advanced Computer Science and Applications* (IJACSA), Vol. 8(7), pp. 164-172, July 2017. https://doi.org/10.14569/IJACSA.2017.080722

- [22] S. Fuada, T. Adiono, A.P. Putra, and Y. Aska, "Noise Analysis in VLC Optical Link based Discrette OP-AMP Trans-Impedance Amplifier (TIA)," *Jurnal of TELKOMNIKA*, Vol. 15(3), pp. 1012-1021, September 2017.

- [23] T. Adiono, Y. Aska, S. Fuada, A.A. Purwita, "Design of an OFDM System for VLC with a Viterbi Decoder," *IEEK Transaction on Smart Processing and Computing* (SPC), Vol. 6(6), pp. 455-465, December 2017. <u>https://doi.org/10.5573/IEIESPC.2017.6.6.455</u>

- [24] T. Adiono, Yulian Y. Aska, A.A. Purwita, S. Fuada, and A.P. Putra, "Modeling OFDM system with Viterbi Decoder Based Visible Light Communication" *Proc. of the Int. Conf.* on Electronic, Information and Communication (ICEIC), Phuket, Thailand, January 2017.

- [25] T. Adiono, and S. Fuada, "Optical Interference Noise Filtering over Visible Light Communication System Utilizing Analog High-Pass Filter Circuit," *Proc. of the 2017 Int. Symp. on Nonlinear Theory and Its Applications* (NOLTA), pp. 616-619, December 2017.

- [26] T. Adiono, and S. Fuada, "Investigation of Optical Interference Noise Characteristics in Visible Light Communication System," *Proc. of the 2017 Int. Symp. on Nonlinear Theory* and Its Applications (NOLTA), pp. 612-615, December 2017.

- [27] T. Adiono, S. Fuada, and R.A. Saputro, "Automatic Gain Control Circuit for Mobility Visible Light Communication System using LM13700" Proc. of IEEE Int. Symposium on Electronics and Smart Devices (ISESD), Yogyakarta, Indonesia, October 2017.

- [28] T. Adiono, S. Fuada, and S. Harimurti, "Bandwidth Budget Analysis for Visible Light Communication Systems utilizing Commercially Available Components," *Proc. of the 10<sup>th</sup> Int. Conf. on Electrical and Electronics Engineering* (ELECO), pp. 1375-1380, December 2017.

- [29] S. Fuada, A.P. Putra, Y. Aska, and T. Adiono, "Noise Analysis of Trans-impedance Amplifier (TIA) in Variety Op Amp for use in Visible Light Communication (VLC) System," *International Journal of Electrical and Computer Engineering* (IJECE), Vol. 8(1), 2018.

- [30] A. Pradana, S. Fuada, and T. Adiono, "Desain dan Implementasi Sistem Visible Light Communication berbasis Pulse Width Modulation," Unpublished.

- [31] T. Adiono, A. Pradana, and S. Fuada "Rancang Bangun Sistem Komunikasi Cahaya Tampak dengan Modulasi 2-PWM berbasis Mikrokontroller," *Unpublished*.

- [32] S. Fuada, T. Adiono, A.P. Putra, Y. Aska, "LED Driver Design for Indoor Lighting and Low-rate Data Transmission Purpose, *Optik-Int. J. for Light and Electron Optics*, Vol. 156, pp. 847-856, 2017, https://doi.org/10.1016/j.ijleo.2017.11.180.

- [33] T. Adiono, R.A. Saputro, M. Luthfi, and S. Fuada, "FPGA Implementation for Real-time File Transfer using Visible Light Communications," *Unpublished*.

- [34] T. Adiono, S. Fuada, and A. Pradana, "Desain dan Realisasi Sistem Komunikasi Cahaya Tampak untuk *Streaming* Teks berbasis PWM," *J. Setrum*, Vol. 6(2), pp. 270-279, Desember 2017.

[35] S. Fuada, A.P. Putra, and T. Adiono, "Short-range Audio Transfer through 3 Watt White LED based on LOS Channels," *Proc. of Int. Conf. on Intellegent Signal Processing and Communication Systems* (ISPACS), pp. 398-403, November 2017. https://doi.org/10.1109/ISPACS.2017.8266511

## 7 Authors

**Trio Adiono (Assoc. Prof. Dr.)** is a senior lecturer of the School of Electrical Engineering and Informatics ITB. He is a member of international conferences (*e.g.* GCCE, ISPACS, APSIPA, ISESD), a head director of University Center of Excellence on Microelectronics, Institut Teknologi Bandung, Indonesia and a chairman of Solid-State Circuits Society (SSCS) Indonesia chapter. He is an author and co-author of 150+ publications (national or international levels).

**Syifaul Fuada (B.A. M.Sc)** is a researcher and engineer in University Center of Excellence on Microelectronics (*www.pme.itb.ac.id/*), Institut Teknologi Bandung, Indonesia. He is the Associate Editor of the journal of INFOTEL and reviewer in several international journals. His research interests include visible light communication system, DSP, IC design, multimedia learning development, instrumentation and discrete analog design. He is a coordinator of VLC research in IC design labs ITB.

**Rosmianto Aji Saputro (B.Eng)** is an embedded system engineer in PT. Xirka Silicon Technology (*www.xirkachipset.com/*), Bandung, Indonesia. Hardware Group Member. Works including device requirement analysis to meet client needs, firmware development, also hardware testing and verification. He has finished several big projects like "Arduino MQTT Library for SIM900 GSM-GPRS Module" in 2016, "Disco Room with Beat Detection" in 2016 and "FPGA-based 1024-bit Pseudorandom Number Generator" in 2014, "Wirelay" in 2014, and many more.

Article submitted 11 December 2017. Final acceptance 23 February 2018. Final version published as submitted by the authors.